100GBASE-LR4 QSFP28 1310nm 10km Módulo Hi-Optel HQSFP28-2L2

Descripciones

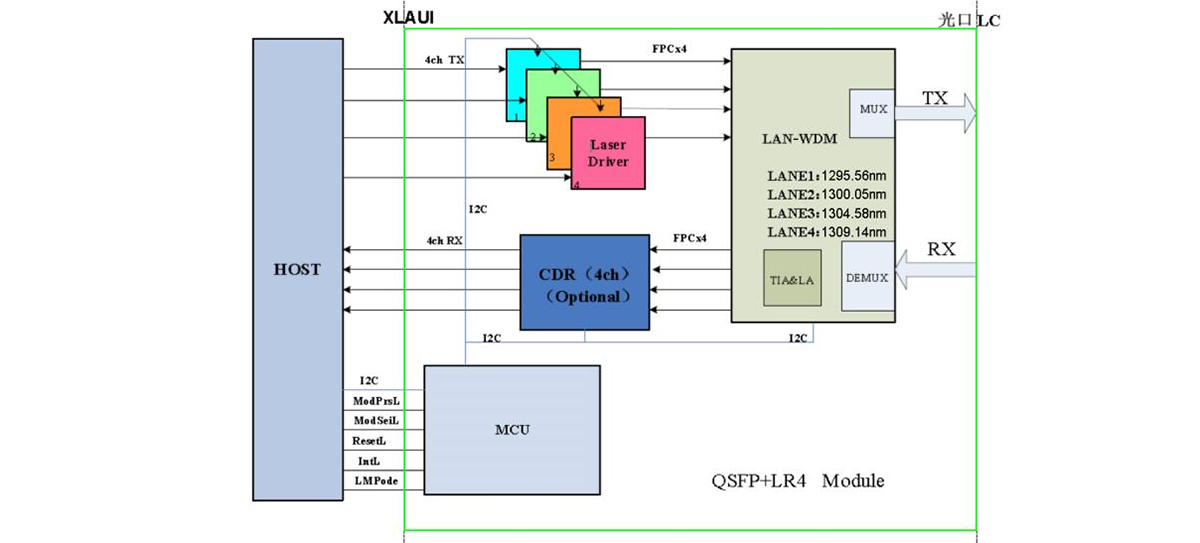

A continuación se muestra un diagrama de bloques del transceptor óptico QSFP28 LR4.

Características

● Admite una velocidad de bits agregada de 103,1 Gb/s

● Interfaz eléctrica reprogramada 4x25,78Gb/s

● Transmisor LAN-WDM basado en DFB de 4x25,78 Gb/s y receptor PIN/TIA

● Longitud máxima del enlace de 10 km enFibra monomodo (SMF)

● Tamaño QSFP28 conectable en caliente

● Receptáculos LC dúplex

● Fuente de alimentación única de 3,3 V

● Disipación de potencia máxima <3,5 W

● Cumple con RoHS-6 y no contiene plomo

● Interfaz de gestión I2C

● Temperatura de funcionamiento de la caja:Comercial: 0°C a +70°C

Solicitud

● Ethernet 100GBASE-LR4 100G

Cumplimiento

● QSFP28 MSA.

●IEEE802.3bm e IEEE802.3ba

●SFF-8679

●RoHS

Interfaz de monitoreo de diagnóstico digital

La función de monitoreo de diagnóstico digital está disponible en QSFP28 LR4. Monitoreo en tiempo real incluye módulotemperatura, voltaje de alimentación del módulo y monitoreo para cada canal transmisor y receptor.

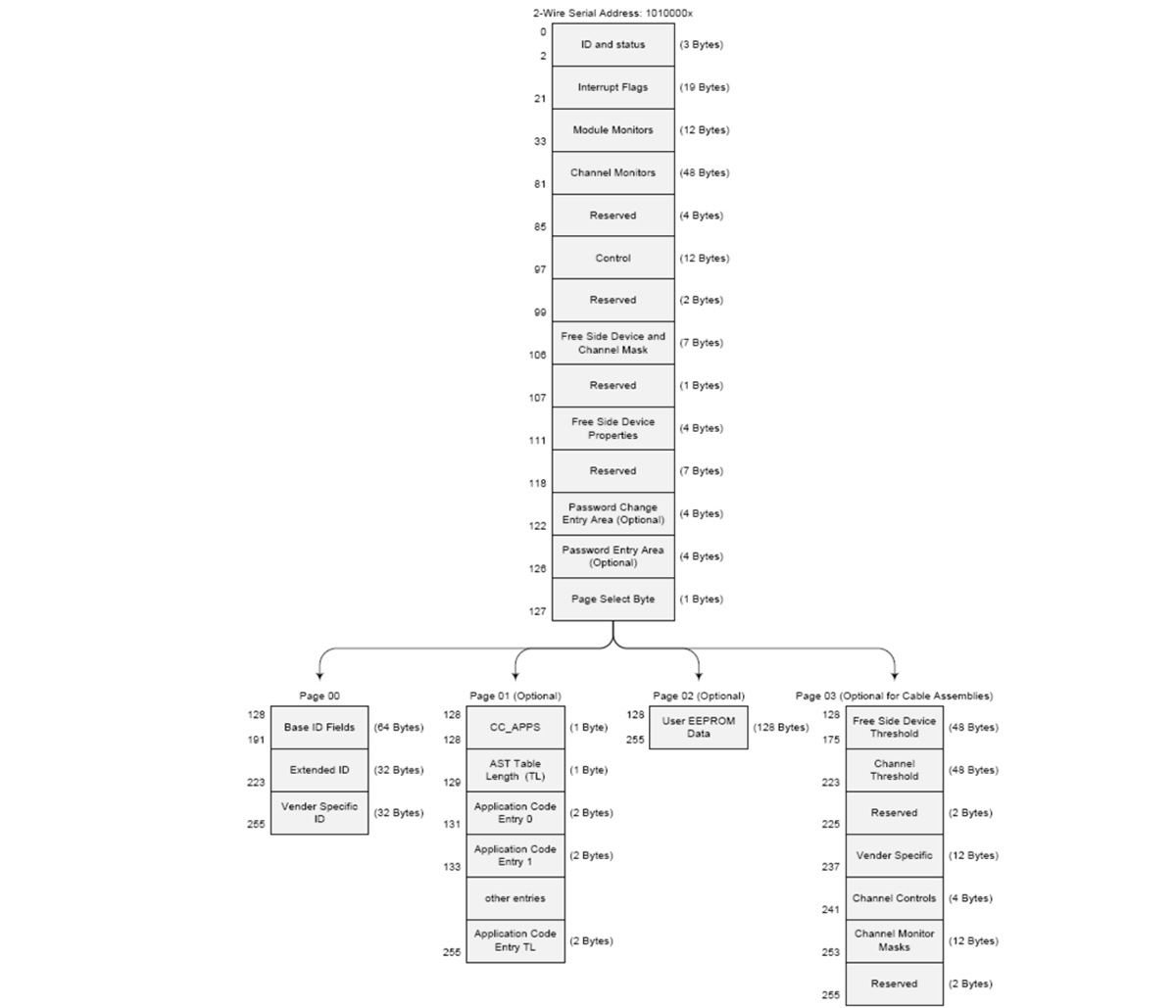

El mapa de memoria para el módulo QSFP28 se utiliza para identificación de serie, monitoreo digital y ciertas funciones de control.

La interfaz es obligatoria para todos los dispositivos QSFP28. La interfaz ha sido diseñada en gran medida a partir del XFP MSA.como se define en INF-8077i Rev.4.0. El mapa de memoria se ha cambiado para dar cabida a 4 ópticas.canales y limitar el espacio de memoria requerido. Se utiliza el enfoque de dirección única tal como se encuentra en XFP. La paginación esSe utiliza para permitir interacciones críticas en el tiempo entre el host y el módulo.

La estructura de la memoria se muestra en la Figura 30. El espacio de la memoria está organizado en una sola página inferior,espacio de direcciones de 128 bytes y múltiples páginas de espacio de direcciones superiores. Esta estructura permite el acceso oportuno adirecciones en la página inferior, por ejemplo, indicadores y monitores de interrupción. Entradas menos urgentes, por ejemplo, ID de serieLa información y los ajustes de umbral están disponibles con la función de selección de página. La estructura también proporcionaampliar la dirección agregando páginas superiores adicionales según sea necesario. Por ejemplo, en la tabla 1, páginas superiores 01 y 02son opcionales. La página superior 01 permite la implementación de la tabla de selección de aplicaciones y la página superior 02 proporcionaEspacio de lectura/escritura del usuario. La página inferior y la página superior 00 siempre se implementan. La página 03 es necesaria si el byte 2,El bit 2 en la página inferior es bajo. Consulte la Tabla 39 para obtener detalles sobre la declaración de las páginas superiores opcionales 01 y 02.

La dirección de interfaz utilizada es A0xh y se utiliza principalmente para datos críticos en el tiempo, como el manejo de interrupciones, para permitir una "lectura única" de todos los datos relacionados con una situación de interrupción. Después de que se haya afirmado una interrupción, IntL, el host puede leer el campo de bandera para determinar el canal afectado y el tipo de bandera.

Tabla 1: Mapa de memoria de diagnóstico digital (descripciones de campos de datos específicos).

| DIRECCIÓN | Descripción | Tipo | Cobre pasivo, cobre activo, óptico activo | Módulo óptico |

| 0 | Identificador (1 Byte) | Sólo lectura | R | R |

| 1-2 | Estado (2 bytes) | Sólo lectura | Ver Tabla 18 | |

| 3-21 | Indicadores de interrupción (19 bytes) | Sólo lectura | Ver Tablas 19-21 | |

| 22-33 | Monitores de módulo (12 Bytes) | Sólo lectura | Ver Tabla 22 | |

| 34-81 | Monitores de canal (48 bytes) | Sólo lectura | Ver Tabla 23 | |

| 82-85 | Reservado (4 Bytes) | Sólo lectura | Reservado | |

| 86-97 | Control (12 Bytes) | Leer/Escribir | Ver Tabla 24 | |

| 98-99 | Reservado (2 Bytes) | Leer/Escribir | Reservado | |

| 100-106 | Máscaras de módulo y canal (7 bytes) | Leer/Escribir | Ver Tabla 25 | |

| 107-118 | Reservado (12 Bytes) | Leer/Escribir | Reservado | |

| 119-122 | Área de entrada de cambio de contraseña (opcional) (4 bytes) | Leer/Escribir | 0 | 0 |

| 123-126 | Área de entrada de contraseña (opcional) 4 bytes | Leer/Escribir | 0 | 0 |

| 127 | Byte de selección de página | Leer/Escribir | R | R |